Компанія IMEC розкрила деталі дорожньої карти по технологічним вузлам, які чекають на нас до 2036 року. Презентація відбулася на Future Summit в Антверпені (Бельгія).

Дослідницька компанія підготувала звіт, в якому розповіли про використання вузлів у передових напівпровідниках (ЦП, ДП, SOC тощо), розкриваючи, що на нас чекає за межами 1 нм.

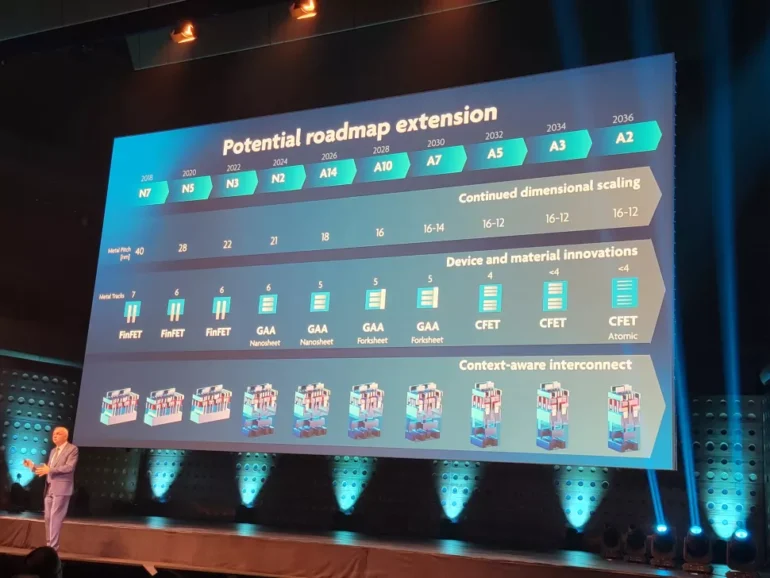

Дорожня карта включає транзистори FinFET, які будуть працювати до 3 нм, до нових нанолистів Gate All Around (GAA) та конструкцій вилкових листів від 2 нм до A7 (сім ангстремів).

Починаючи з 1 нм, вузли процесу починають вимірюватися «ангстремами». 10 ангстрем дорівнюють 1 нм, тому вузли розміром менше ніж 1 нм будуть поставлятися з A7. Це станеться з 2030 року.

Транзистори Gate All Around (GAA)/Nanosheet дебютують у 2024 році з 2-нм вузлом, замінивши FinFET, які використовуються у сучасних удосконалених чипах. Intel вже показала мікросхеми RibbonFET із чотирма аркушами, у яких використовуються різні варіанти цієї транзисторної технології.

На літографічних машинах EUV 4-го покоління з апертурою 0,33 можна використовувати мультипатерни (більше однієї експозиції на шар), щоб створювати чипи на 2 нм та вище. Але через повторний друк одного шару збільшується ймовірність появи дефектів, що призведе до зниження продуктивності, збільшення виробництва та витрат.

Машини п’ятого покоління з апертурою 0,55 зможуть створювати менші структури за одну експозицію, що збільшить швидкість виробництва понад 200 пластин на годину. Такі інструменти для масового виробництва з’являться вже 2026 року, а першу літографічну машину з високою апертурою завершать у першій половині 2023 року. Компанія ASML витратила на створення $400 млн.

IMEC очікує, що транзистори GAA/nanosheet та forksheet будуть використовуватися аж до вузлів A7 (менше ніж 1 нм). До 2032 року будуть використовуватися комплементарні польові транзистори (CFET), а до 2036 року фірма очікує, що використовуватимуться транзистори CFET з атомними каналами.

Можливість збільшити щільність транзисторів і зменшити розмір вузла матиме вирішальне значення для підвищення продуктивності обчислень і додавання нових функцій. Подальше збільшення щільності транзисторів вимагатиме удосконалених процесів Back End of Line (BEOL). Вони зосереджені на з’єднанні транзисторів разом, забезпечуючи як зв’язок (сигнали), так і подачу живлення.

IMEC називає ці методи підвищення вторинної щільності «підсилювачами масштабування», оскільки вони сприяють збільшенню щільності та продуктивності транзисторів, навіть якщо вони не пов’язані безпосередньо з розміром/розміщенням транзисторів.

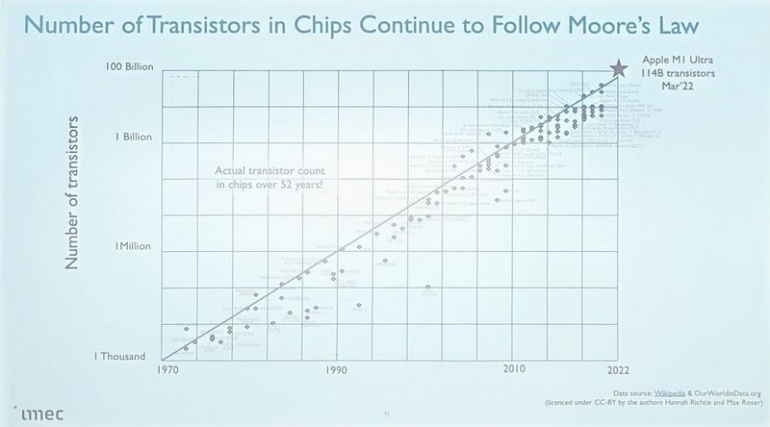

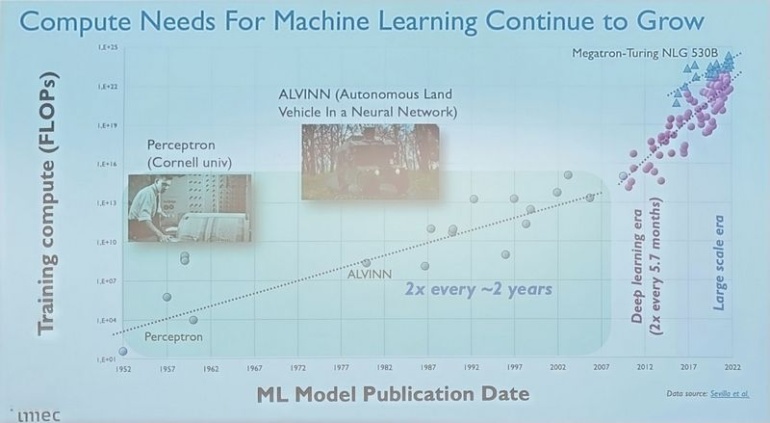

IMEC вважає, що закон Мура продовжуватиме виконуватись, що стане проблемою для всієї галузі, особливо у зв’язку з появою машинного навчання. З розвитком вузлів попит на електроенергію збільшується, а витрати різко зростають. Магнітні ворота можуть стати альтернативою, адже галузь невблаганно рухається до квантових обчислень.

Повідомити про помилку

Текст, який буде надіслано нашим редакторам: