Система ШІ з нуля розробила повноцінне ядро процесора RISC-V усього за 12 годин.

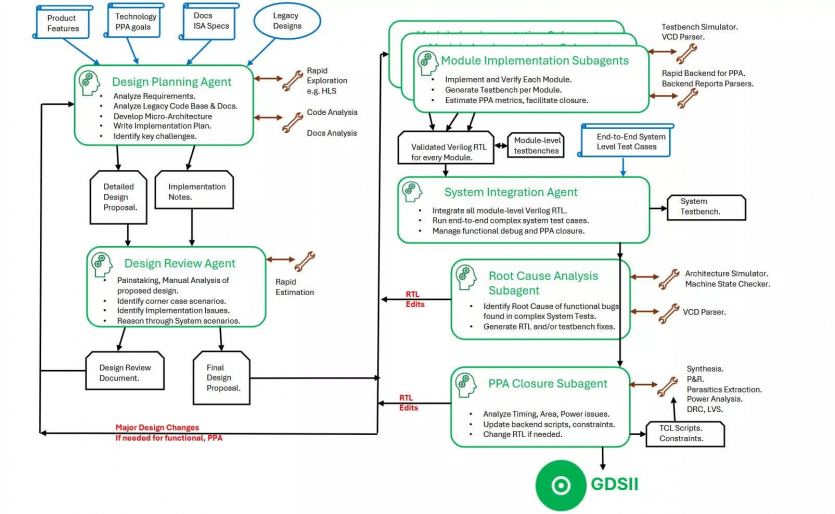

Це вперше, коли автономний агент ШІ самостійно створив робочий процесор від специфікації до GDSII. Як і звичайні інженери, штучний інтелект дотримувався традиційного циклу проєктування — проєктування, створення, тестування та доопрацювання.

Однак він робив це цілком самостійно, не покладаючись на окремі інструменти автоматизації для кожного етапу. Процесор під назвою VerCore був створений стартапом Verkor.io, який займається розробкою мікросхем з використанням ШІ Design Conductor.

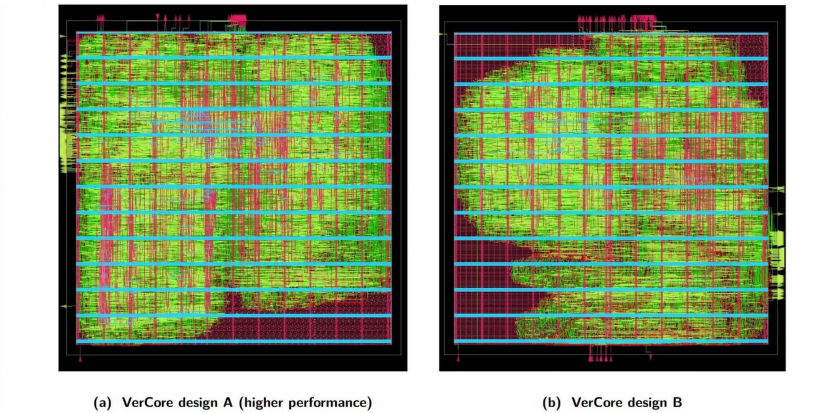

Згідно з оприлюдненим технічним документом, VerCore отримав п’ятиступеневу конвеєрну архітектуру з послідовним виконанням операцій та тактовою частотою 1,48 ГГц. Зазначається, що чип отримав 3261 бал в бенчмарку CoreMark, спеціалізованому застосунку для вимірювання продуктивності мікроконтролерів та процесорів у вбудованих системах.

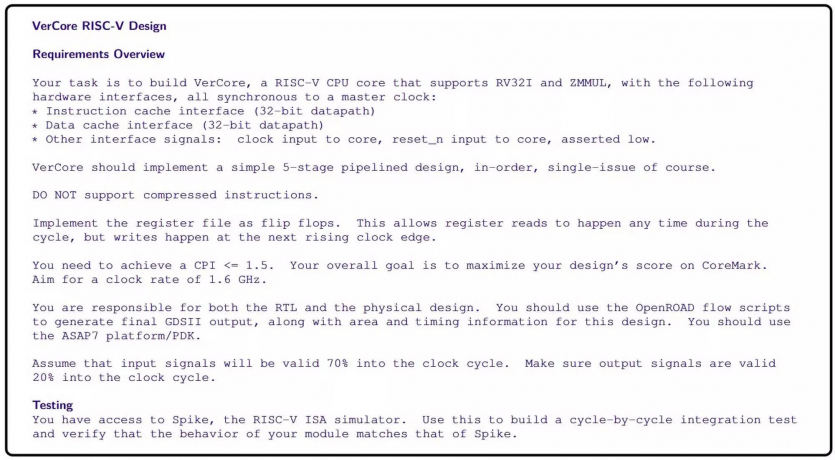

Результати, звісно, доволі скромні, VerCore навряд чи може конкурувати з процесором початкового рівня Intel Celeron SU2300 2011 року. При цьому Design Conductor це не LLM, а інструмент, який обмежує LLM, змушуючи їх дотримуватись певного набору інструкцій для досягнення поставленої задачі. У цьому випадку проводилась робота зі специфікацією обсягом 219 слів, наданою інженерами VerCore.

Результатом стало отримання файлу GDSII, який можна використати для створення реального ядра CPU за допомогою ПЗ EDA. Фізично VerCore не існує, його працездатність була підтверджена у симуляції з використанням еталонного симулятора архітектури RISC-V, Spike.

Топологія була розроблена з використанням ASAP7 PDK, відкритого академічного комплекту проєктування, який модулює 7-нм техпроцес. Цей прогнозний PDK був розроблений інженерами з Університету Аризони спільно з ARM Research. Він доступний на GitHub за ліцензією BSD 3-Clause.

Verkor планує опублікувати всі відповідні проєктні файли до кінця місяця. Це дозволить незалежним розробникам та стороннім компаніям перевірити заяви про можливості цього інструменту ШІ. Компанія також планує провести демонстрацію процесу створення VerCore на конференції з автоматизації проєктування FPGA в Каліфорнії в липні.

Раніше ми писали, що Anthropic випустила нову модель ШІ Claude Opus 4.7 для просунутого вайбкодингу та мультимодальних завдань. Дослідники з Університету Північної Кароліни представили новий інструмент на базі ШІ CacheMind для допомоги розробникам у підвищенні продуктивності CPU.

Від місяців до годин: як ШІ радикально прискорює створення нових чипів NVIDIA

Джерело: TechSpot

Повідомити про помилку

Текст, який буде надіслано нашим редакторам: